隨著三孩政策的深入和家庭育兒消費(fèi)的升級(jí),嬰童用品市場(chǎng)持續(xù)展現(xiàn)出蓬勃的活力與巨大的潛力。在這一背景下,選擇一個(gè)值得信賴的品牌進(jìn)行加盟或代理,成為許多創(chuàng)業(yè)者實(shí)現(xiàn)財(cái)富夢(mèng)想的優(yōu)選路徑。圣安琪嬰童用品作為業(yè)內(nèi)知名品牌,以其完善的產(chǎn)品體系、成熟的運(yùn)營模式和強(qiáng)大的品牌支持,吸引了眾多投資者的目光。本文將為您全面解析圣安琪嬰童用品的加盟、代理及相關(guān)信息。

一、 品牌實(shí)力:圣安琪嬰童用品的核心優(yōu)勢(shì)

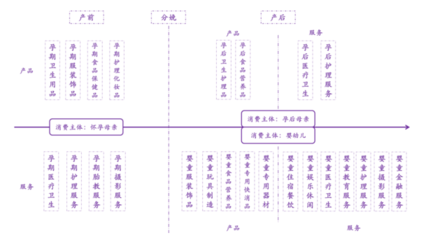

圣安琪嬰童用品專注于為0-6歲嬰幼兒提供安全、健康、高品質(zhì)的用品與器材。其產(chǎn)品線覆蓋廣泛,包括但不限于:

- 日常護(hù)理用品:如奶瓶、奶嘴、洗浴用品、護(hù)膚系列等。

- 服飾寢具:四季童裝、睡袋、床品等,注重面料安全與舒適度。

- 出行裝備:嬰兒推車、汽車安全座椅、背帶腰凳等。

- 玩具與早教器材:益智玩具、健身架、學(xué)步車等,促進(jìn)嬰幼兒智力與體能發(fā)展。

- 喂養(yǎng)用品:餐具、水杯、輔食制作工具等。

品牌堅(jiān)持以嚴(yán)格的質(zhì)量標(biāo)準(zhǔn)和安全認(rèn)證為基石,深入洞察現(xiàn)代父母的精細(xì)化育兒需求,在設(shè)計(jì)上兼顧實(shí)用性、時(shí)尚感與科技元素,從而在市場(chǎng)中建立了良好的口碑與品牌信譽(yù)。

二、 合作模式:加盟與代理詳解

圣安琪為不同投資能力和市場(chǎng)經(jīng)驗(yàn)的創(chuàng)業(yè)者提供了靈活的合作方案。

- 連鎖加盟:這是圣安琪主要的擴(kuò)張模式。加盟商將獲得品牌授權(quán)的完整店面形象、運(yùn)營系統(tǒng)及產(chǎn)品供應(yīng)支持。總部通常會(huì)提供從選址評(píng)估、店面設(shè)計(jì)、開業(yè)策劃、人員培訓(xùn)到后期營銷的全套扶持,幫助加盟店快速步入正軌,實(shí)現(xiàn)標(biāo)準(zhǔn)化、專業(yè)化運(yùn)營。加盟模式更側(cè)重于終端零售網(wǎng)點(diǎn)的建設(shè)與品牌形象的統(tǒng)一。

- 區(qū)域代理:針對(duì)具有較強(qiáng)渠道開發(fā)和管理能力的投資者,圣安琪開放區(qū)域代理權(quán)。代理商負(fù)責(zé)在指定區(qū)域內(nèi)(如一個(gè)城市或省份)進(jìn)行品牌推廣、產(chǎn)品分銷,并可能發(fā)展和管理下屬的二級(jí)經(jīng)銷商或零售終端。此模式要求代理商擁有更豐富的商業(yè)資源和市場(chǎng)開拓能力,但相應(yīng)的市場(chǎng)空間和盈利潛力也更大。

無論選擇哪種模式,圣安琪總部旨在與合作伙伴建立長期共贏的關(guān)系,通過持續(xù)的產(chǎn)品更新、市場(chǎng)培訓(xùn)和政策激勵(lì),共同開拓嬰童消費(fèi)市場(chǎng)。

三、 加盟支持體系:堅(jiān)實(shí)的創(chuàng)業(yè)后盾

選擇圣安琪,意味著您不是孤軍奮戰(zhàn)。品牌為合作伙伴構(gòu)建了多維度的支持體系:

- 產(chǎn)品支持:穩(wěn)定的供應(yīng)鏈保障,提供具有市場(chǎng)競爭力的優(yōu)質(zhì)產(chǎn)品,并定期推出新品。

- 培訓(xùn)支持:涵蓋產(chǎn)品知識(shí)、銷售技巧、門店管理、客戶服務(wù)及促銷活動(dòng)的系統(tǒng)化培訓(xùn)。

- 運(yùn)營支持:提供成熟的運(yùn)營管理手冊(cè)、POS系統(tǒng)及庫存管理指導(dǎo),助力日常高效運(yùn)營。

- 營銷支持:共享品牌廣告資源,提供開業(yè)促銷、節(jié)日活動(dòng)方案及線上線下整合營銷指導(dǎo)。

- 區(qū)域保護(hù):合理的區(qū)域規(guī)劃,保障加盟商或代理商的獨(dú)家經(jīng)營權(quán),避免惡性競爭。

四、 如何獲取官方信息與聯(lián)系

在考慮加盟或代理前,通過官方渠道進(jìn)行全面了解和實(shí)地考察至關(guān)重要。

- 圣安琪嬰童用品官網(wǎng):官方網(wǎng)站是獲取品牌最權(quán)威、最全面信息的第一入口。通常,官網(wǎng)會(huì)詳細(xì)展示品牌故事、產(chǎn)品系列、加盟政策、成功案例以及新聞動(dòng)態(tài)。建議有意向者仔細(xì)瀏覽官網(wǎng)的“加盟合作”或“投資合作”相關(guān)欄目。

- 圣安琪嬰童用品電話:官網(wǎng)一般會(huì)公布全國統(tǒng)一的招商咨詢熱線。通過電話咨詢,您可以初步了解最新的加盟政策、投資門檻、支持細(xì)節(jié),并可預(yù)約前往總部或現(xiàn)有門店進(jìn)行實(shí)地考察。

重要提示:在聯(lián)系時(shí),請(qǐng)務(wù)必核實(shí)信息的官方性,謹(jǐn)防虛假信息。建議直接訪問通過可靠搜索引擎找到的官網(wǎng),并撥打官網(wǎng)公示的聯(lián)系電話。

五、 市場(chǎng)前景與投資建議

嬰童用品行業(yè)屬于剛性需求市場(chǎng),且消費(fèi)趨向品牌化、品質(zhì)化。圣安琪定位清晰,產(chǎn)品組合豐富,若能借助其品牌勢(shì)能與運(yùn)營體系,在選址得當(dāng)、經(jīng)營得法的情況下,有望獲得可觀回報(bào)。

給潛在投資者的建議:

- 自我評(píng)估:清晰自身的資金實(shí)力、興趣所在及本地市場(chǎng)情況。

- 深入調(diào)研:充分利用官網(wǎng)、電話等渠道了解圣安琪,并務(wù)必進(jìn)行實(shí)地考察,與總部負(fù)責(zé)人面對(duì)面溝通。

- 市場(chǎng)分析:對(duì)計(jì)劃開店或代理區(qū)域的競爭對(duì)手、目標(biāo)客群、消費(fèi)水平做詳細(xì)調(diào)研。

- 理性決策:仔細(xì)閱讀加盟或代理合同,明確雙方權(quán)責(zé),結(jié)合自身情況做出審慎投資決定。

圣安琪嬰童用品為創(chuàng)業(yè)者提供了一個(gè)進(jìn)入嬰童產(chǎn)業(yè)的高起點(diǎn)平臺(tái)。通過其專業(yè)的加盟代理體系,創(chuàng)業(yè)者可以大幅降低獨(dú)立創(chuàng)業(yè)的風(fēng)險(xiǎn),更快地分享市場(chǎng)成長紅利。立即通過官方渠道開啟您的咨詢之旅,或許就是邁向成功的第一步。